pp. 35-56

# N-Channel MOSFET Small-Signal Darlington Pair based Low-Power Wide-Band Amplifier

## Pratima Soni, Syed Shamroz Arshad, Geetika Srivastava and SachchidaNand Shukla

Department of Physics and Electronics Dr. Ram Manohar Lohia Avadh University, Ayodhya, UP, India Email: <u>sachida.shukla@gmail.com</u>

#### (Received January 10, 2023, Accepted February 20, 2023)

N-channel identical MOSFETs based Abstract: Small-Signal Darlington pair amplifiers under triple transistor topology are simulated at GPDK 180nm, 90nm, and 45nm process technologies in Cadence Virtuoso and Spectre simulation tool. At 180nm technology, amplifier amplifies 1µV-100mV range AC signal with voltage gain (11.656), current gain (105.971), bandwidth (39.4747 GHz), power consumption (25.6708 mW) and THD (0.000031 %). Similarly, at 90nm technology, amplifier is capable of amplifying 1µV-2V ranging AC signal with voltage gain (1.02605), current gain (97.704), bandwidth (91.8932 GHz), power consumption (0.0038  $\mu$ W) and THD (0.0000034%). However, at 45nm technology, amplifier produces voltage gain (0.0481), current gain (32.2163), higher cut-off frequency (691.367 Hz), power consumption (17.5314 mW) and THD (0.000000004%) with AC signal amplifying range 10  $\mu$ V-1V. This work also addresses the narrow bandwidth issue of reference amplifier, PNP Sziklai pair amplifier, and poor response issue of proposed amplifier at 45nm technology at higher frequency. Proposed amplifiers are also implemented in Quadrupole topology to test the behavior of the amplifiers. Layout of the proposed amplifiers captures small-area of 2.8858  $\mu$ m<sup>2</sup> of (1.59  $\mu$ m X 1.815  $\mu$ m) dimensions and gives same pre and post layout results. Effect of w/l ratio, effect of C<sub>L</sub>, effect of different biasing parameters, small-signal AC analysis, temperature dependency and phase variations are among the few studies pursued for the proposed amplifiers. Frequency range suggests their possible application in high pass filter, wireless communication receivers and preamplifiers stages of ECG and seismographs.

**Keywords:** MOSFET, Cadence, Triple transistor topology, Darlington Pair, Small-signal amplifier, Quadrupole Topology.

#### 1. Introduction

Common-Source MOSFETs amplifiers are generally used to amplify small-signal audio range signals due to its high input impedance, low output impedance, high current gain and voltage gain just greater than unity<sup>1</sup>. However, the Darlington pair, comprises of two identical bipolar transistors, produces high current gain and wide bandwidth at a low frequency, therefore they are being used for high data rate communication system<sup>2</sup>. Darlington pairs are the ideal choice for the applications where high current gain and higher linearity are required<sup>3</sup>. Many small-signal amplifier circuits are examined using Common Source MOSFETs in a Darlington pair configuration<sup>4</sup>. However, the fundamental issue with this setup is that it generates narrow bandwidth signals with high power consumption and high harmonic distortions<sup>5</sup>. Many changes have been suggested over the years to address this issue, such as the insertion of biasing resistances, the use of hybrid active device combinations, or the substitution of Sziklai pairs for Darlington pairs in double- or triple-transistor topologies<sup>6</sup>. In this series, amplifiers with three identical MOSFETs and a few additional resistances and capacitances are proposed, which not only reduces output distortions but also solves the problem of a narrow bandwidth<sup>7-9</sup>.

In this paper, three amplifier circuits are proposed using Cadence Virtuoso and Spectre simulation at GPDK 180nm, 90nm, and 45nm process technologies<sup>10-12</sup>. These circuits are based on identical N-channel MOSFETs with a Darlington pair topology, making them suitable for both low- and high-frequency applications<sup>13-14</sup>. Better results in terms of bandwidth, power consumption, and THD are obtained when comparing these amplifiers with the reference amplifier circuit, which is based on commercial Power MOSFETs<sup>15</sup>. Proposed amplifiers are also tested on various scales such as effect of w/l ratio, effect of C<sub>L</sub>, effect of temperature, Quadrupole topology, Layout and Post-layout simulation, variation of different biasing elements, small-signal AC analysis, Phase variation, determination of performing range for each parameter, and behavior of amplifiers under different conditions. The key merits of the proposed amplifiers are the elimination of the narrow bandwidth issue with reference and PNP Sziklai pair amplifiers as well as the poor response issue with Darlington pair amplifiers at higher frequencies.

## 2. Experimental Circuit Description

#### 2.1. Circuit Details

Present article comprises the simulation and analysis of N-Channel MOSFET Small-Signal Darlington pair amplifier at GPDK (Generic Process

Device Kits) 180nm, 90nm and 45nm process technologies using Cadence Virtuoso and Spectre Simulation<sup>16</sup>.

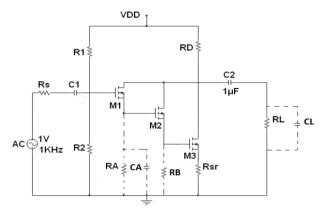

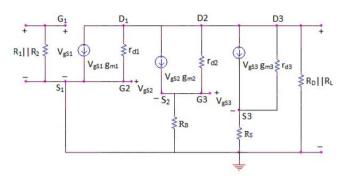

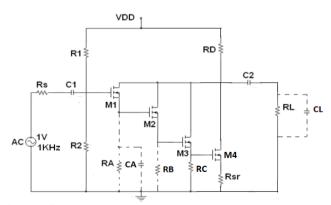

Figure 1. Circuit Design of the Reference and Proposed Amplifiers

Triple transistor topology based Small-Signal Darlington pair amplifier is treated here as "Reference amplifier<sup>15</sup>." Simulated on PSpice simulation software at nearly  $2\mu$ m technology, this amplifier uses three identical nMOS Power transistors with an additional resistor R<sub>A</sub> and capacitor C<sub>A</sub> connected between source of first transistor M<sub>1</sub> to ground<sup>17</sup>. However, modified version of the said amplifier is proposed in this paper at 180nm, 90nm and 45nm technologies using Cadence Virtuoso and Spectre simulation and referred here as Proposed Amplifier-1, Proposed Amplifier-2 and Proposed Amplifier-3 respectively.

At 180nm technology, Proposed amplifier-1 includes an extra resistor  $R_B$  joined between source of second transistor  $M_2$  to ground along with resistor  $R_A$  and capacitor  $C_A$  connected between source of first transistor  $M_1$  to ground. Similarly, Proposed amplifier-2 at 90nm technology performs better with two additional resistors  $R_A$  and  $R_B$  connected between source of  $M_1$  and  $M_2$  to ground respectively. However, at 45nm technology, Proposed amplifier-3 requires only one additional resistor  $R_B$  connected between source of  $M_2$  to ground and load capacitor  $C_L$  across  $R_L$ . Additionally, similar performance is obtained if this resistor is switched to source of  $M_1$  to ground. Basic circuit diagram for the mentioned amplifiers is shown in Figure 1. Position of  $R_A$ ,  $C_A$ ,  $R_B$  and  $C_L$  varies from one amplifier to another; therefore, they are shown by dotted lines.

#### 2.2. Circuital Parameter and Software Details

Table 1 enlists the simulation parameters of nMOS transistors used in Reference and Proposed amplifiers.

| MOSFET Model Parameters                                                         | s Reference Proposed Amplifiers |                        |                       | s                     |

|---------------------------------------------------------------------------------|---------------------------------|------------------------|-----------------------|-----------------------|

|                                                                                 | Amplifier                       | At 180nm<br>Technology | At 90nm<br>Technology | At 45nm<br>Technology |

| Model Name of M <sub>1</sub> , M <sub>2</sub> and M <sub>3</sub><br>Transistors | IRF150                          | nmos1                  | gpdk090_nmos1v        | g45n1svt              |

| Cell Name of Each Transistors                                                   |                                 | Nmos                   | nmos1v                | nmos1v                |

| W (Channel Width)                                                               | 0.3m                            | 2µm                    | 120nm                 | 120nm                 |

| L (Channel Length)                                                              | 2µm                             | 180nm                  | 100nm                 | 45nm                  |

| T (Threshold)                                                                   |                                 | 800nm                  | 120nm                 | 120nm                 |

| MW (S/D Metal Width)                                                            |                                 | 400nm                  | 120nm                 | 60nm                  |

| VTO (Zero-bias threshold voltage)                                               | 2.831                           | 0.48                   | NaN                   | NaN                   |

| GAMMA (Bulk Threshold Parameter)                                                | 0                               | 0.666                  | NaN                   | NaN                   |

| KP (Transconductance)                                                           | 20.53E-06                       | 0.490                  | NaN                   | NaN                   |

| PHI (Surface Potential)                                                         | 0.6                             | 0                      | 0                     | 0                     |

| IS (Bulk p-n saturation current)                                                | 194E-18                         | NaN                    | NaN                   | NaN                   |

| CBD (Bulk-drain zero bias p-n capacitance)                                      | 3.229E-09                       | 0                      | 0                     | 0                     |

| RD (Drain ohmic resistance)                                                     | 1.031E-03                       | 0                      | 0                     | 0                     |

| RG (Gate ohmic resistance)                                                      | 13.89                           |                        |                       |                       |

| RDS (Drain-source shunt resistance)                                             | 444.4E+03                       |                        |                       |                       |

| CGSO (Gate-source overlap capacitance)                                          | 9.027E-09                       | 370E-12                | NaN                   | NaN                   |

| CGDO (Gate-drain overlap capacitance)                                           | 1.679E-09                       | 370E-12                | NaN                   | NaN                   |

Table 1. Simulation Parameters of MOSFETs

## Table 2. Circuit Components

| Circuit Components                             | Reference<br>Amplifier | Proposed<br>Amplifier-1<br>at 180nm | Proposed<br>Amplifier-2<br>at 90nm | Proposed<br>Amplifier-3<br>at 45nm |

|------------------------------------------------|------------------------|-------------------------------------|------------------------------------|------------------------------------|

| Rs (Source Resistance)                         | 250Ω                   | 10Ω                                 | 10Ω                                | 10Ω                                |

| R <sub>1</sub> (Biasing Resistance)            | 1.4MΩ                  | 1MΩ                                 | 20ΜΩ                               | 800KΩ                              |

| R <sub>2</sub> (Biasing Resistance)            | 1MΩ                    | 100KΩ                               | 1MΩ                                | 600KΩ                              |

| R <sub>D</sub> (Drain Resistance)              | 1ΚΩ                    | 3ΚΩ                                 | 30KΩ                               | 4ΚΩ                                |

| R <sub>SR</sub> (Source Biasing Resistance)    | 100KΩ                  | 10Ω                                 | 100KΩ                              | 10Ω                                |

| R <sub>A</sub> (Additional Biasing Resistance) | 300Ω                   | 600Ω                                | 10Ω                                | Unavailable                        |

| R <sub>B</sub> (Additional Biasing Resistance) | Unavailable            | 600Ω                                | 10Ω                                | 10Ω                                |

| R <sub>L</sub> (Load Resistance)               | 10KΩ                   | 10KΩ                                | 10KΩ                               | 500Ω                               |

| C <sub>1</sub> (Input Capacitor)               | 10µF                   | 10µF                                | 10µF                               | 10µF                               |

| C <sub>2</sub> (Output Capacitor)              | 1µF                    | 1µF                                 | 1µF                                | 100nF                              |

| C <sub>A</sub> (Additional Capacitors)         | 100uF                  | 100uF                               | Unavailable                        | Unavailable                        |

| V <sub>CC</sub> (Biasing Supply)               | +15V                   | +15V                                | +15V                               | +15V                               |

Observations for the Reference as well as Proposed amplifiers are made for 1mV, 1KHz AC input sin wave with +15 Volt DC power supply. Values of the circuit components used in the mentioned amplifiers are listed in Table 2.

## 3. Results and Discussion

## **3.1. Performance Parameters**

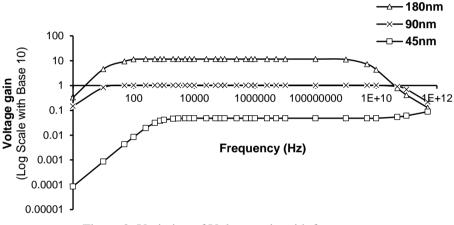

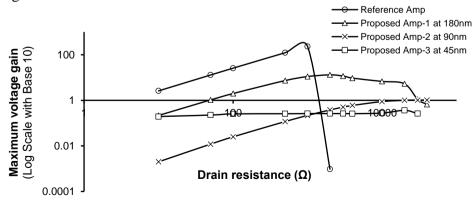

Various performance parameters of the Reference and Proposed amplifiers at 180nm, 90nm and 45nm technologies are recorded in Table 3 at room temperature with the aid of Cadence Virtuoso and Spectre Simulation<sup>18,19</sup>. Figure 2 shows how the voltage gain of the proposed amplifiers varies with respect to frequency for various technologies.

Figure 2. Variation of Voltage gain with frequency

Table 2 suggests that when technology is scaled down to improve the speed of MOSFETs, voltage and current gain of the proposed amplifiers simultaneously reduces<sup>20</sup>. However, bandwidth, power consumption, output referred noise and THD gets improved<sup>21</sup>. This happens because w/l ratio of the MOSFETs reduces with reducing technology, therefore transconductance  $g_m$  of transistor also decreases as per the relation,  $g_m = k' (w / l)(v_{gs} - v_t)$ . Since, the voltage gain of the proposed amplifier is directly proportional to  $g_m$  hence, voltage gain also decreases<sup>22</sup>. In addition, at 45nm technology, due to the Zener break down at source/substrate junction and Short Channel Effect (channel length becomes equal to the depletion-layer width of source), response curve of voltage gain produces severe distortion<sup>23</sup>. Additionally, in comparison to the reference amplifiers, proposed amplifiers show wider bandwidth, lower power consumption, lower THD and lower output referred noise at 1KHz frequency at the cost of low gain<sup>24</sup>.

| Performance Parameters                              | Reference<br>Amplifier | Proposed<br>Amplifier<br>at 180nm | Proposed<br>Amplifier<br>at 90nm | Proposed<br>Amplifier<br>at 45nm |

|-----------------------------------------------------|------------------------|-----------------------------------|----------------------------------|----------------------------------|

| Amplifier Current Gain AIGA                         | 2652.4                 | 105.971                           | 97.704                           | 32.2163                          |

| Upper Cut Off Frequency $F_H$ (for $A_{IGA}$ )      | 37.140 Hz              | 148.422 MHz                       | 747.693 MHz                      | 5.096 GHz                        |

| Lower Cut Off Frequency $F_L$ (for $A_{IGA}$ )      | 26.204 Hz              | 20.834 Hz                         | 7.2467 Hz                        | 674.715 Hz                       |

| Band-Width Bw (for AIGA)                            | 10.936 Hz              | 148.421 MHz                       | 747.692 MHz                      | 5.096 GHz                        |

| Amplifier Voltage Gain Avga                         | 232.12                 | 11.656                            | 1.02605                          | 0.0481                           |

| Upper Cut Off Frequency $F_H$ (for $A_{VGA}$ )      | 4.805<br>KHz           | 39.4748 GHz                       | 91.8933 GHz                      |                                  |

| Lower Cut Off Frequency $F_L$ (for $A_{VGA}$ )      | 379.32 Hz              | 20.8392 Hz                        | 7.2385 Hz                        | 691.367 Hz                       |

| Band-Width Bw (for AvgA)                            | 4.426<br>KHz           | 39.4747 GHz                       | 91.8932 GHz                      |                                  |

| Unity Gain Band-Width (for $A_{VGA}$ )              | 854.899<br>KHz         | 428.525 GHz                       | 24.7712 GHz                      |                                  |

| Device Voltage Gain Avgd                            | 235.596                | 11.66                             | 2.3638                           | 0.275                            |

| Device Current Gain AIGD                            | 2387.8                 | 575.693 M                         | 11.94 K                          | 540.1466                         |

| Input Referred Noise                                | 2.1021                 | 83.372                            | 164.378                          | 67.9104                          |

|                                                     | nV/Hz                  | $\mu V / \sqrt{Hz}$               | $\mu V / \sqrt{Hz}$              | $\mu V / \sqrt{Hz}$              |

| Output Referred Noise                               | 480.085                | 179.1                             | 45.444                           | 2.7872                           |

|                                                     | nV/Hz                  | $\mu V / \sqrt{Hz}$               | $\mu V/\sqrt{Hz}$                | $\mu V/\sqrt{Hz}$                |

| Power Gain PA (in dB-Watt)                          | 57.893                 | 30.917                            | 20.0108                          | 11.9021                          |

| Output Voltage Phase Difference $\theta^{O}$        | -168.921               | -178.594                          | -179.576                         | -147.9787                        |

| Phase Margin of Voltage gain<br>θM                  |                        | 98.4079                           | 12.7321                          | Can't be<br>computed             |

| Total Harmonic Distortion THD                       | 0.93%                  | 0.000031%                         | 0.0000034%                       | 0.00000004%                      |

| Total Power Consumption, $P_W$                      | 167 mW                 | 25.6708 mW                        | 0.0038 µW                        | 17.5314 mW                       |

| Input Signal Voltage                                | 1 mV at<br>1KHz        | 1 mV at 1<br>KHz                  | 1 mV at<br>1KHz                  | 1 mV at 1KHz                     |

| Permissible Range of Input<br>Signal Voltage        | 0.1 mV-2<br>mV         | 1 μV-100mV                        | 1 μV-2V                          | 10 μV-1V                         |

| Slew rate of output voltage                         |                        | 0.390 V/µs                        | 0.0413 V/µs                      | 0.875 V/µs                       |

| Current across Source<br>Resistance I <sub>RS</sub> | 760.107<br>nA          | 11 nA                             | 1.0501 nA                        | 2.991 nA                         |

| Current across Load Resistance I <sub>RL</sub>      | 24.03 µA               | 1.1958 μA                         | 103.398 nA                       | 89.4039 nA                       |

| Voltage across source resistance V <sub>RS</sub>    | 1 mV                   | 1 mV                              | 1 mV                             | 1 mV                             |

| Voltage across load resistance $V_{RL}$             | 240.28<br>mV           | 11.96 mV                          | 1.0343 mV                        | 44.70 μV                         |

| Power Spectral Density                              |                        | 17.35 nV <sup>2</sup> /Hz         | 1.02 nV <sup>2</sup> /Hz         | 8.7256 pV <sup>2</sup> /Hz       |

| Transfer Function                                   |                        | 11.66 V/V                         | 1.02605 V/V                      | 48.1742 mV/V                     |

| Chip Area                                           |                        | 2.8858 μm <sup>2</sup>            |                                  |                                  |

Table 3 Comparative Table of Performance Parameters

Refer Table 3. Since higher the phase margin (Phase shift at 0dB gain), more stable the amplifier will be<sup>25</sup>. Therefore, proposed amplifier-1 at 180nm technology produces highest phase margin (98.4079°), hence it is more stable than rest of the amplifier's configurations. At 90nm technology, proposed amplifier-2 has widest AC signal amplification range, lowest power consumption and nearly 180° phase shift. Similarly, proposed amplifier-3 at 45 nm technology emerges with highest slew rate (rate of change of output voltage) which must be high in order to produce maximum undistorted output voltage swing<sup>26</sup>. In addition, this configuration also produces lowest output referred noise and lowest THD (approx. tending towards zero) at 1KHz frequency and widest frequency band from 674.715 Hz to 5.096 GHz.

Large difference between current gain  $A_{IG}$  and device current gain  $A_{IGD}$  of all the proposed amplifiers can be interpreted because the current at resistance  $R_D$  suddenly drops to a non-significant value which causes sudden decrease in the overall current gain of the amplifier.

Figure 2 shows that response curve of the proposed amplifier-3 at 45nm technology becomes distorted beyond 100 THz frequency and looks more or less like high-pass filter circuit with cut-off frequency  $f_{H}$ =691.367 Hz which indicates potential application of this amplifier as a "Low-Power High-Pass Filter" in generalized biomedical signal processing circuits<sup>27</sup>. However, poor frequency response nature of this amplifier is further removed by adding load capacitor  $C_L=1pF$  across  $R_L$ . It is also to be noted that value of the load capacitor must lie within the range  $10nF \le C_L \le 1$  fF. Additionally, proposed amplifier-1 at 180nm technology and Proposed amplifier-2 at 90nm technology produces frequency band from 20.8392 Hz to 39.4747 GHz and 7.2385 Hz to 91.8933 GHz respectively along with low power consumption, low THD and low noise which made them suitable to be used as LNA in Transceiver design in wireless communication system<sup>28</sup>. Main contributions of the proposed amplifier are that they remove the narrow band problem of reference amplifier. Also, proposed amplifier-1 at 180nm, proposed amplifier-2 at 90nm and proposed amplifier-3 at 45nm with C<sub>L</sub> successfully eliminate poor frequency response problem of small-signal Darlington pair amplifier at higher frequencies.

## 3.2. Effect of *w/l* Ratio on the Amplifier Performance

Variation in w/l ratio of MOSFETs draws significant impact over the performance parameters, therefore variation of the performance parameters with respect to variation in w/l ratio of respective MOSFETs is studied at 180nm, 90nm and 45nm technologies respectively<sup>29</sup>.

## A. At 180nm Technology

At 180nm technology, maximum limit of channel width w is 50µm and minimum is 400nm with default value of 2µm. Similarly, maximum limit of channel length l is infinite whereas minimum limit is 180nm with default value of 180nm. Variation of parameters with w/l ratio is listed in Table 4.

| W/L Ratio   | Voltage gain | Current Gain | Bandwidth   | Power        |

|-------------|--------------|--------------|-------------|--------------|

|             |              |              |             | Consumption  |

| 400nm/180nm | 4.9975       | 45.437       | 92.7044 GHz | 21.481 mW    |

| 500nm/180nm | 5.7867       | 52.612       | 88.4591 GHz | 21.954 mW    |

| 750nm/180nm | 7.3563       | 66.883       | 82.7117 GHz | 22.955 mW    |

| 2µm/180nm   | 11.656       | 105.971      | 39.4747 GHz | 25.670 mW    |

| (Default)   |              |              |             |              |

| 50µm/1µm    | 14.64        | 133.039      | 1.201 GHz   | 28.200 mW    |

|             |              |              |             | (Distortion) |

Table 4: Variation of parameters at 180nm Technology

## B. At 90nm Technology

At 90nm technology, channel length varies in the range  $100nm \le L \le 21.68\mu m$  with default value of 100nm whereas channel width varies in the range  $120nm \le W \le 30\mu m$  with default value of 120nm. Their variation with parameters is listed in Table 5.

W/L Ratio **Current Gain** Voltage gain Bandwidth Power Consumption 120nm/100nm (Default) 1.0260 97.7041 91.8932 GHz  $0.0038 \,\mu W$ 500nm/100nm 2.3959 288.033 41.554 GHz 5.9642 mW 750nm/250nm 3.10698 295.1454 988.103 MHz 3.8595 mW 1µm/500nm 232.122 877.926 MHz 2.4886 2.05 mW 21.68µm/30µm 0.494 14.99 1.2139 GHz 166.52 W

Table 5: Variation of parameters at 90nm Technology

## C. At 45nm Technology

At 45nm technology, default value of channel length is 45nm and it can not be greater than 10 $\mu$ m and less than 45nm. Similarly, channel width can not be less than 120nm and greater than 10 $\mu$ m with default value of 120nm. Their variation with parameters is enlisted in Table 6.

| W/L Ratio            | Voltage gain | Current Gain | Bandwidth   | Power<br>Consumption |

|----------------------|--------------|--------------|-------------|----------------------|

| 120nm/45nm (Default) | 0.040        | 32.2163      | 5.096 GHz   | 17.5314 mW           |

| 500nm/100nm          | 0.036        | 18.09        | 1.4755 GHz  | 25.781 mW            |

| 750nm/250nm          | 0.019        | 10.57        | 1.11214 GHz | 26.197 mW            |

| 1µm/500nm            | 0.011        | 4.6151       | 639.584 MHz | 33.3507 mW           |

| 10µm/10µm            | 0.001        | 1.621        | 7.5502 MHz  | 28.92 mW             |

**Table 6:** Variation of parameters at 45nm Technology

Refer Table 4, 5 and 6. When w/l ratio of MOSFETs at 180nm and 90nm technology is increased; voltage gain, current gain and power consumption simultaneously increases whereas bandwidth reduces. Contrarily, at 45nm technology; voltage gain, current gain and bandwidth reduces with increasing value of w/l ratio however power consumption increases.

# 3.3. Observation under Different Conditions

# A. At 180nm Technology

- 1. When all the extra added resistors  $R_A$ ,  $R_B$  and capacitor  $C_A$  are removed from the proposed amplifier-1, voltage gain and current gain both drops to 0.047 and 0.427 respectively. Apart from this, response curve of voltage gain starts behaving as high pass filter with cut-off frequency  $f_H$ =5.74255 KHz. Also, power consumption shoots up to 54.693 mW and output voltage and output current transient responses distorted badly. Therefore, it is essential to include these resistors and capacitors to maintain amplifying nature.

- 2. When  $R_A$  and  $C_A$  are removed keeping  $R_B$  fixed, Voltage and current gain decreases to 0.263 and 2.3997 with distorted output transient waveforms. In addition to it, power consumption also increases to 53.667 mW.

- 3. Similarly, When  $R_B$  is removed keeping  $R_A$  and  $C_A$  fixed, output voltage transient responses become distorted with voltage and current decreases to 0. 958 and 8.7108 respectively along with 56.44 mW Power Consumption.

- 4. If  $C_S=10$ uF is added across  $R_{SR}$ , no effect is reported on parameters.

- 5. If  $C_A$  is removed keeping  $R_A$  and  $R_B$  fixed, voltage and current gain decreases to 4.3646 and 39.682 respectively with undistorted transient response. Moreover, minor decrement is seen in bandwidth (37.2891 GHz) and power consumption (25.7372 mW).

- 6. If  $C_A$  is added across  $R_B$  keeping  $R_A$  fixed, voltage gain, current gain and bandwidth decreases to 7.6479, 69.507 and 31.688 GHz respectively. However, power consumption remains unaltered (25.7372 mW).

# B. At 90nm Technology

1. When all the added resistors  $R_A$  and  $R_B$  are removed from the proposed amplifier-2, response curve of current gain is distorted and reaches to 0.692 whereas voltage gain provide poor response at higher frequency and reaches to 0.998 with distorted output current and voltage waveforms. Power consumption also reduces to 1.6043mW. Therefore, it is essential to include these resistors and capacitors.

- 2. When  $R_A$  is removed keeping  $R_B$  intact, both voltage as well as current gain curve produces poor frequency responses at higher frequencies. Additionally, current gain reaches to 62.528, voltage gain to 0.656 and power consumption to 4.2183mW.

- 3. \*\*However, when R<sub>B</sub> is removed keeping R<sub>A</sub> intact, response of voltage gain becomes poor at higher frequency but both, voltage, and current gain increase to their respective peak values 1.1263 and 107.244 respectively.

- 4. If  $C_S=10 \mu$ F is added across  $R_{SR}$ , voltage gain, current gain and bandwidth decreases to 0.993, 94.646 and 79.3294 GHz respectively. However, power consumption becomes higher (3.8621 mW).

# C. At 45nm Technology

- 1. When the added resistor  $R_B$  is removed from proposed amplifier-3, voltage gain becomes very much small and reaches to 0.004 whereas current gain decreased to 2.9151 and shows poor response at higher frequency. However, power consumption becomes very high and reaches to 12.83 W.

- 2. If the position of resistor  $R_B$  is changed i.e., if it is connected between  $M_1$  to ground, same result is obtained. This is the unique result which is not generally found in small-signal amplifiers.

- 3. If both  $R_A$  and  $R_B$  are added, current and voltage gain decreased to 0.329 and 0.015 respectively whereas power consumption increases to 25.47 mW.

- 4. If  $C_S=10$ uF is added across  $R_{SR}$ , all parameters remain unchanged.

# 3.4. Performing Range of the Circuit Components

At 180nm technology (Proposed amplifier-1), minimum value of amplifier voltage gain A<sub>VGA</sub> is received at R<sub>S</sub>=960K $\Omega$  (A<sub>VG-MIN</sub>=1.0083) and maximum value at R<sub>S</sub>=1 $\Omega$  (A<sub>VG-MAX</sub>=11.6566) with meaningful amplification in  $1\Omega \le R_S \le 1.3M\Omega$  range. Similarly, values of R<sub>1</sub> and R<sub>2</sub> must be kept within the range 500K $\Omega \le R_1 \le 1M\Omega$  and  $20K\Omega \le R_2 \le 600K\Omega$  respectively. Moreover, maximum, and minimum limit of R<sub>D</sub> in order to produce amplification is 50K $\Omega$  and 38K $\Omega$  respectively. Also, value of R<sub>A</sub> and R<sub>B</sub> must be kept less than or equal to 20K $\Omega$ . In addition, value of the C<sub>A</sub> must lie within the range 100mF  $\le C_A \le 10$ uF because when the C<sub>A</sub> exceeds 10uF, voltage response curve produces poor response at higher frequency.

At 90nm technology (Proposed amplifier-2), value of  $R_S$  must be kept less than or equal to 20K $\Omega$ . Also, lower limit for  $R_1$  is 50M $\Omega$ , however there is no maximum limit for  $R_1$  because after a critical value, voltage gain remains constant at increasing value of  $R_1$  whereas boundary condition for  $R_2$  is 200K $\Omega \le R_2 \le 1M\Omega$ . Moreover, meaningful amplification corresponds to  $R_D$  is received within the range  $20K\Omega \le R_D \le 100K\Omega$ . In addition, value of added resistances  $R_A$  and  $R_B$  must be less than or equal to  $2K\Omega$  to receive amplification.

At 45nm technology (Proposed amplifier-3), during observation an important finding is received that when the value of the source resistor  $R_S$  exceeds 50K $\Omega$ , poor response problem of this particular amplifier at higher frequency is removed without adding any load capacitor across  $R_L^{30}$ . Current gain reaches its minimum value 1.00473 at  $R_1$ =500K $\Omega$  and maximum value 44.7162 at  $R_1$ =1M $\Omega$ . Similarly,  $R_2$  provides purposeful amplification in the 400K $\Omega \le R_2 \le 1M\Omega$  range. In the same way, current gain reaches its minimum value 8.9139 at  $R_D$ =1K $\Omega$  and maximum value 30.5528 at  $R_D$ =10K $\Omega$ . However, boundary limit for  $R_B$  should be  $R_B \le 1K\Omega$  in order to receive distortion-less response.

## 3.5. Effect of Load Capacitor CL

Effect of load capacitor  $C_L$  on the performance of the amplifiers has also been studied at 180nm, 90nm and 45nm technologies respectively using Cadence Virtuoso and Spectre simulation<sup>21,22</sup>.

At 180nm technology, proposed amplifier-1 produces meaningful amplification for the range  $10\mu F \le C_L \le 1nF$ . For example, at  $C_L=1nF$ , performance parameters for proposed amplifier-1 are -  $A_{VG}=11.656$  B<sub>W</sub>= 136.144 MHz A<sub>IG</sub>=105.9708 and Total Power Consumption=25.6707mW. Similarly, at  $C_L=10\mu F$ , performance parameters are as follows-  $A_{VG}=1.01836$  B<sub>W</sub>= 180.614 Hz A<sub>IG</sub>=9.4388 Total Power Consumption=25.6315 mW.

Similarly, at 90nm technology, proposed amplifier-2 works effectively with the load capacitor  $C_L$  in the range  $10\mu F \le C_L \le 1pF$ . At  $C_L=1pF$ , performance parameters for the proposed amplifier-2 are -  $A_{VG}=0.048$  B<sub>W</sub>= 432.171 MHz A<sub>IG</sub>=32.2162 Total Power Consumption=17.531 mW. Similarly, at  $C_L=10\mu F$ , parameters for the proposed amplifier-2 obtained are as follows -  $A_{VG}=0.002$  B<sub>W</sub>= 95.112 Hz A<sub>IG</sub>=1.72783 Total Power Consumption=17.5314 mW.

It is noteworthy that the proposed amplifier-3 at 45nm technology produces poor response at higher frequency  $(\geq 100 \text{THz})^{23,24}$ . Therefore, inclusion of load capacitor as a basic circuital element in this amplifier removes the poor response problem at higher frequency<sup>25</sup>. Performing range of C<sub>L</sub> for producing distortion-less response is  $10n\text{F} \leq \text{C}_{L} \leq 1\text{fF}$ . Parameters at C<sub>L</sub>=1fF is - A<sub>VG</sub>=01.02605 B<sub>W</sub>= 22.5698 GHz A<sub>IG</sub>=97.704 Total Power Consumption=3.8620 mW. Similarly, at C<sub>L</sub>=10nF, parameters are - A<sub>VG</sub>=1.02138 B<sub>W</sub>= 1.98 Hz A<sub>IG</sub>=97.2593 Total Power Consumption=3.8620

mW. In addition, poor response problem of this amplifier at higher frequency is also resolved when  $C_L$  reaches 100fF.

Observations indicate that at higher values of load capacitors within the specified range, proposed amplifiers produce narrow bandwidth i.e., 180.614 Hz for proposed amplifier-1, 95.112 Hz for proposed amplifier-2 and 95.112 Hz for proposed amplifier-3. Therefore, these amplifiers may be used for the amplification of  $\delta$ ,  $\theta$ ,  $\alpha$ ,  $\beta$  and  $\gamma$  waves released by human brain if used at preamplifier stage in EEG signal acquisition circuit. These amplifiers may also be used as pre-amplifier in seismograph for the amplification of seismic waves emerged during earthquake<sup>26,27</sup>.

# 3.6. Variational Effect of Amplifier with Different Parameters

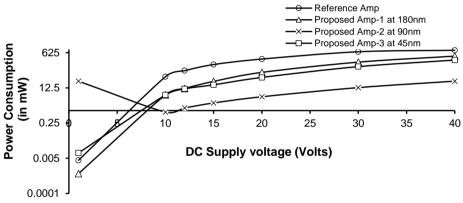

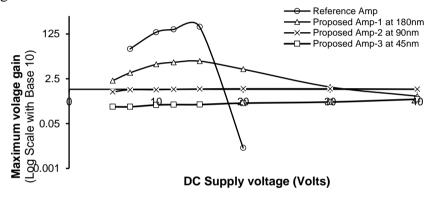

## 3.6.1. Effect of DC Supply Voltage on Total Power Consumption

Variation of total power consumption of all the amplifiers with respect to DC supply voltage is shown in Figure  $3^{28,29}$ .

Figure 3. Variation of Power Consumption with DC Supply Voltage

It has been seen that power consumption is directly proportional to the DC supply voltage. For the reference amplifier, power consumption decreases with increasing DC supply voltage up to 10V<sup>15</sup>. However, beyond this value, power consumption starts increasing with increasing DC supply voltage. Contrarily, for the proposed amplifiers, power consumption increases with increasing DC supply voltage.

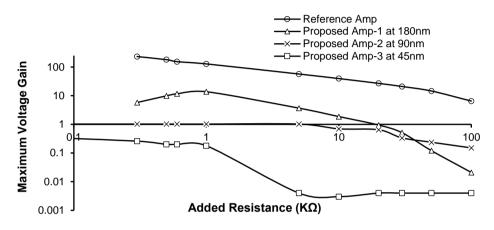

## 3.6.2. Variation of Voltage Gain with Added Resistance

Variation of the voltage gain of all the amplifiers with respect to added resistance is also shown in Figure  $4^{30}$ .

Voltage Gain of the reference amplifier and proposed amplifier-3 at 45nm technology decreases with increasing value of added resistance  $R_A^{15}$ .

However, for proposed amplifier-1 at 180nm technology, voltage gain initially increases with increasing value of  $R_A$  up to  $R_A/R_B=1K\Omega$ . But beyond this value, it starts decreasing with increasing  $R_A$  and produces distortion in the response curve. Similarly, for the proposed amplifier-2 at 90nm technology, voltage gain remains constant up to  $R_A=5K\Omega$  and thereafter starts decreasing with increasing  $R_A$ . In addition, when  $R_A \ge 5K\Omega$ , severe distortion is received in the voltage gain response curve.

Figure 4. Variation of Voltage Gain with Added Resistance

Boundary condition for added resistance  $R_A$  in the proposed amplifier-1 is  $R_A$ ,  $R_B \leq 20 K\Omega$ , proposed amplifier-2 is  $R_A$ ,  $R_B \leq 2 K\Omega$  and proposed amplifier-3 is  $R_B \leq 3 K\Omega$ .

## 3.6.3. Variation of Voltage Gain with Drain Resistance

Variation of voltage gain with respect to drain resistance is depicted in Figure 5<sup>10,11</sup>.

Figure 5. Variation of Voltage Gain with Added Resistance

Reference and Proposed amplifier-1 at 180nm technology increases with increasing value of  $R_D$  up to  $R_D=1K\Omega$  and decreases thereafter<sup>15</sup>. Similarly, voltage gain of the proposed amplifier-2 at 90nm technology, increases with increasing  $R_D$ . However, voltage gain of the proposed amplifier-3 at 45nm technology, almost remains constant with increasing value of  $R_D$ .

Performing range of proposed amplifier-1 corresponds to  $R_D$  is  $38K\Omega \le R_D \le 500K\Omega$ , proposed amplifier-2 is  $20K\Omega \le R_D \le 100K\Omega$  and proposed amplifier-3 is  $1K\Omega \le R_D \le 10K\Omega$ .

## 3.6.4. Variation of Voltage Gain with DC Supply Voltage

Variation of voltage gain with respect to DC Supply Voltage is depicted in Figure 6<sup>12,13</sup>.

Figure 6. Variation of Voltage Gain with DC Supply Voltage

Reference amplifier switches-ON at  $V_{CC}=7$  Volts and its voltage gain rises non-linearly with increasing value of supply voltage up to  $V_{CC}=15$  Volts and decreases sharply above this value<sup>15</sup>. Similarly, proposed amplifier-1 at 180nm technology switches-ON at  $V_{CC}=2$  Volts and its voltage gain increases non-linearly upto  $V_{CC}=15$  Volt and decreases thereafter. However, proposed amplifier-2 at 90nm technology switches-ON at  $V_{CC}=15$  Volt and remains almost constant with increasing value of  $V_{CC}$ . Similarly, Voltage gain of the proposed amplifier-3 at 45nm technology, increases with a slow pace with increasing DC supply voltage.

## 3.6.5. Variation of Voltage Gain with Source Resistance

Variation of Voltage gain as a function of source resistance has also been studied for all the amplifiers under consideration<sup>14</sup>. It is found that Voltage gain of the proposed amplifiers almost remain constant with respect to variation in  $R_{SR}$ . However, voltage gain of the reference amplifier initially increases up to  $R_{SR}=5K\Omega$  and acquire saturation trend at higher values of  $R_{SR}$ <sup>15</sup>.

# **3.7. Effect of Temperature Dependency**

Impact of temperature on the performance of the proposed amplifiers have also been studied and respective observation corresponds to proposed amplifier-1, proposed amplifier-2 and proposed amplifier-3 have been recorded in Table 7, Table 8 and Table 9 respectively<sup>16</sup>.

| Temperature |              | Proposed Amplifier-1 at 180nm |             |                      |  |  |

|-------------|--------------|-------------------------------|-------------|----------------------|--|--|

| (°C)        | Voltage Gain | Current Gain                  | Bandwidth   | Power<br>Consumption |  |  |

| -20         | 13.7544      | 125.054                       | 39.5432 GHz | 25.1131 mW           |  |  |

| 0           | 12.7663      | 116.07                        | 39.4551 GHz | 25.3720 mW           |  |  |

| 10          | 12.329       | 112.098                       | 39.414 GHz  | 25.4887 mW           |  |  |

| 27          | 11.656       | 105.971                       | 39.3747 GHz | 25.6708 mW           |  |  |

| 50          | 10.852       | 98.6656                       | 39.2014 GHz | 25.8920 mW           |  |  |

| 80          | 9.9408       | 90.3816                       | 39.0423 GHz | 26.1535 mW           |  |  |

Table 7. Variation of parameters of Proposed amplifier-1 with Temperature

Table 8. Variation of parameters of Proposed amplifier-2 with Temperature

| Temperature | Proposed Amplifier-2 at 90nm |              |             |                      |  |

|-------------|------------------------------|--------------|-------------|----------------------|--|

| (°C)        | Voltage Gain                 | Current Gain | Bandwidth   | Power<br>Consumption |  |

| -20         | 1.14315                      | 108.8566     | 95.754 GHz  | 4.1232 mW            |  |

| 0           | 1.09555                      | 104.3231     | 94.067 GHz  | 4.0103 mW            |  |

| 10          | 1.07047                      | 101.9345     | 93.129 GHz  | 3.9549 mW            |  |

| 27          | 1.02605                      | 97.704       | 91.8932 GHz | 3.8000 mW            |  |

| 50          | 0.962                        | 91.6167      | 90.0549 GHz | 3.7382 mW            |  |

| 80          | 0.876                        | 83.4149      | 88.291 GHz  | 3.5824 mW            |  |

Table 9. Variation of parameters of Proposed amplifier-3 with Temperature

| Tomporatura         |              | Proposed Amplifier-3 at 45nm |             |                      |  |  |

|---------------------|--------------|------------------------------|-------------|----------------------|--|--|

| Temperature<br>(°C) | Voltage Gain | Current Gain                 | Bandwidth   | Power<br>Consumption |  |  |

| -20                 | 0.026        | 17.7848                      | 5.12114 GHz | 23.8528 mW           |  |  |

| 0                   | 0.025        | 17.9364                      | 5.1412 GHz  | 23.8489 mW           |  |  |

| 10                  | 0.020        | 18.8935                      | 5.1737 GHz  | 23.7453 mW           |  |  |

| 27                  | 0.048        | 32.6163                      | 5.1960 GHz  | 17.5314 mW           |  |  |

| 50                  | 0.045        | 30.282                       | 5.2145 GHz  | 16.9186 mW           |  |  |

| 80                  | 0.042        | 27.768                       | 5.2741 GHz  | 16.0865 mW           |  |  |

Refer Table 7 and 8. Voltage gain, current gain, and bandwidth of proposed amplifier-1 at 180nm technology and Proposed amplifier-2 at 90nm technology decreases as the temperature range increases. However, power consumption of the proposed amplifier-1 increases whereas for proposed

amplifier-2, it decreases with increasing temperature. This happens because drain-source resistance of the composite unit rises with temperature which in turn reduces the voltage gain, current gain and bandwidth<sup>15</sup>.

Table 9 shows that when the temperature of proposed amplifier-3 at 45nm technology increases, bandwidth simultaneously increases whereas power consumption decreases. However, current gain initially increases up to  $27^{\circ}$ C and starts decreasing beyond this value and voltage gain varies in zig-zag manner. Output coupling capacitor C<sub>2</sub> at proposed amplifier-3 bears low capacitance (of the order of 100nF value) which causes reduction in effective circuit capacitance which consequently widens the bandwidth with increasing temperature<sup>17</sup>.

## 3.8. Phase Variation

Phase shift of output current of proposed amplifier-1 at 180nm, proposed amplifier-2 at 90nm and proposed amplifier-3 at 45nm technology with respect to input current is listed in Table  $10^{18,19}$ .

| Frequency | Phase Difference                  | Phase Difference of Output Current with input current in $\theta^{\circ}$ |                                  |  |  |  |

|-----------|-----------------------------------|---------------------------------------------------------------------------|----------------------------------|--|--|--|

|           | Proposed Amplifier-<br>1 at 180nm | Proposed Amplifier-<br>2 at 90nm                                          | Proposed Amplifier-<br>3 at 45nm |  |  |  |

| 1 Hz      | -77.4827                          | -97.3488                                                                  | -87.37745                        |  |  |  |

| 10 Hz     | -99.7668                          | -144.3467                                                                 | -90.73734                        |  |  |  |

| 100 Hz    | -165.7883                         | -176.0042                                                                 | -100.1353                        |  |  |  |

| 1 KHz     | -178.7123                         | -179.5814                                                                 | -149.7504                        |  |  |  |

| 10 KHz    | -179.8589                         | -179.9594                                                                 | -176.7059                        |  |  |  |

| 100 KHz   | -179.9857                         | -179.9959                                                                 | -179.6623                        |  |  |  |

| 1 MHz     | -180.0003                         | -180.0003                                                                 | -179.9667                        |  |  |  |

| 10 MHz    | -180.0153                         | -180.0069                                                                 | -179.9975                        |  |  |  |

| 100 MHz   | -180.1539                         | -180.0698                                                                 | -180.008                         |  |  |  |

Table 10. Phase Variation with Frequency

Refer Table 10. At operating frequency, proposed amplifier-1 produces highest phase difference (-179.5814°) than all other amplifier configurations. Also, proposed amplifier-1 and Proposed amplifier-2 produces 180° output phase shift in the frequency range 1 MHz-100 MHz. Similarly, proposed amplifier-3 produces phase shift at 100 MHz frequency. However, reference amplifier produces 180° output current phase shift at around 1.38 KHz frequency<sup>15</sup>.

# **3.9.** Mathematical Analysis

Small-signal AC equivalent circuit for the Proposed Amplifier-1 at 180nm is shown in Figure  $7^{20,21}$ .

Figure 7. Small Signal AC Circuit of Proposed amplifier-1

Input impedance of this circuit  $(R_1||R_2)$  is 90909.09  $\Omega$  which is much higher than its output impedance  $(R_L||R_D)$  which is 2307.692  $\Omega$ . Similar to the reference amplifier circuit, nMOS transistor M<sub>2</sub> are also treated here as absent as output current of transistor M<sub>2</sub> is zero<sup>15</sup>. Therefore, equation for the AC voltage gain is given by

$$A_{VG} = \frac{-g_{m1} \left(1 + g_{m3} R_S - \frac{R_S}{r_{d3}}\right)}{\frac{1}{R_o} + \frac{1}{R_o} \left(g_{m3} R_S - \frac{R_S}{r_{d3}}\right)}$$

where  $R_o = R_L || R_{D.}$

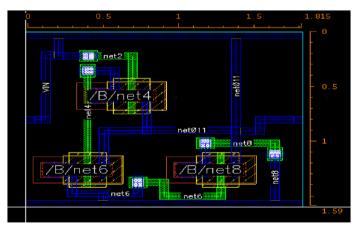

## 3.10. Layout and Post-layout Simulation

Figure 8 depicts the Layout of the proposed amplifier-1 at 180nm technology is also designed using Layout XL Editor tool<sup>12</sup>.

Figure 8. Layout of Proposed amplifier-1 at 180nm Technology

Area of the layout is around 2.8858  $\mu$ m<sup>2</sup> (1.59  $\mu$ m X 1.815  $\mu$ m). All the MOSFETs are taken as 'Integrated' rather than 'Detached' because in each

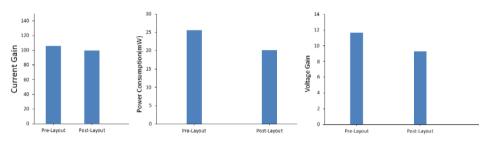

MOSFETs, substrate is directly connected to the source<sup>23</sup>. Horizontal rail is applied at GND and  $V_{DD}$  pins to avoid overlapping whereas IN and OUT pins are fixed at left and right corners respectively<sup>24</sup>. Dimension of M<sub>1</sub> is 0.68µm X 0.955µm whereas for M<sub>2</sub> and M<sub>3</sub>, it is 0.39µm X 0.28µm and 1.275µm X 0.28µm respectively. DRC and LVS run shows no errors and give almost same pre and post layout simulation results under acceptable percentage variation range<sup>15</sup>. As compared to pre-layout simulation, post-layout simulation result of current gain (100.004), voltage gain (9.330) and power consumption (20.133mW) shows 5.79391%, 22.1672% and 24.1805% respectively. Graphical representation of pre and post layout simulation results is shown in Figure 9.

Figure 9. Pre and Post Layout Simulation Results

# 3.11. Proposed Amplifier's Performance under Quadrupole Arrangement

Rather than just the triple transistor topology, proposed amplifiers are also tested with the Quadrupole transistor topology (having four identical MOSFETs) to see how it behaves in different circuit structures. This topology was first proposed by *Hassen* in 2013<sup>14</sup>.

Figure 10. Proposed amplifier under Quadrupole Topology

In this circuit, we have inserted another identical nMOS transistor  $M_4$  whose gate is joined with the source of  $M_3^{17,18}$ . It also employs one added resistor  $R_C=10\Omega$  connected between source of  $M_3$  to ground with distinct value of the load resistor  $R_L=1K\Omega$ . Figure 10 shows the proposed amplifier under Quadrupole topology. Comparison of parameters at 180nm technology in Triple Transistor topology and proposed Quadrupole topology is listed in Table 11.

| Parameters             | Under Quadrupole           | Under Triple               |

|------------------------|----------------------------|----------------------------|

|                        | Topology at 180nm          | Transistor at 180nm        |

| Voltage gain           | 6.9708                     | 11.656                     |

| Low Cut-off Frequency  | 23.667 Hz                  | 20.8392 Hz                 |

| High Cut-off Frequency | 44.7954 GHz                | 39.4748 GHz                |

| Bandwidth              | 44.7953 GHz                | 39.4747 GHz                |

| Current gain           | 633.775                    | 105.971                    |

| Power Consumption      | 22.0444 mW                 | 25.6708 mW                 |

| Output Noise           | 10.466 $\mu V / \sqrt{Hz}$ | 179.1 $\mu V / \sqrt{Hz}$  |

| Input Noise            | 1.50197 μV/√ <i>Hz</i>     | $83.372 \mu V / \sqrt{Hz}$ |

| THD                    | 0.000011%                  | 0.000031%                  |

Table 11. Comparative Table of Parameters under Quadrupole Topology

Table 11 clearly shows that proposed amplifier under quadrupole topology produces high current gain, wide bandwidth, low THD, low output and input noise, low THD, and low power consumption than triple transistor topology at the expense of low voltage gain<sup>19</sup>. Therefore, this topology could serve as a basis for further investigation on the proposed amplifiers to give them more prominence.

### 4. Conclusion

Triple Transistor Toplogy based Small-signal Darlington pair amplifier circuits with identical NMOS transistors available at GPDK 180nm, 90nm and 45nm process technologies are analyzed in this paper using Cadence Virtuoso and Spectre simulation tool. Narrow bandwidth problem of reference amplifier and PNP Sziklai pair amplifier are removed by the proposed amplifiers alongwith consuming low power and producing low THD.

It is also found that as the technology is scaled down, number of passive components in the circuit decreases simultaneously which causes reduction in voltage and current gain and increment in bandwidth. Poor frequency response problem of the amplifier at 45nm technology is removed by adding  $C_L$  across  $R_L$  and exceeding the value of  $R_S$  beyond 50K $\Omega$ . Inclusion of  $C_L$  in

the proposed amplifiers within the specified range helps them to operate in low frequency range (<100Hz) for the amplification of seismic waves and alpha, beta, gamma and delta waves released by human brain.

Proposed amplifiers are also implemented in Quadrupole topology which shows improved results than triple transistor topology. With small-area of 2.8858  $\mu$ m<sup>2</sup> having dimensions of 1.59  $\mu$ m and 1.815  $\mu$ m, proposed amplifiers show same pre and post layout simulation results which validate the amplifiers in 180nm technology. Analysis of the proposed amplifiers suggest their use in high pass filter and as LNA in transceiver design in wireless communication system.

## References

- 1. Muneer A. Hashem; Analysis and Design of BJT Differential Amplifier, 5<sup>th</sup> International Conference on Engineering Technology and its Application (IICETA), (2022), 227-232, DOI: 10.1109/IICETA54559.2022.9888597.

- V. Van Cuong, T. Meguro, S. Ishikawa, T. Maeda, H. Sezaki and S. I. Kuroki; Amplifier based on 4H-SiC MOSFET Operation at 500°C for Harsh Environment Application, *IEEE Transaction on Electron Devices*, 69(8) (2022), 4194-4199, DOI: 10.1109/TED.2022.3184663.

- 3. Crippa *et al.*; Next-Generation Hybrid RF Front-End with MoS<sub>2</sub>-FET Supply Management Circuit, CNT-FET Amplifiers, and Graphene Thin-Film Antennas, *Electronics*, 11(22) (2022), 3708. DOI: 10.3390/electronics11223.

- Adornes, Cristina Missel, Deni Germano Alves Neto, Márcio Cherem Schneider, and Carlos Galup-Montoro; Bridging the gap between design and simulation of low-voltage CMOS circuits, *Journal of Low Power Electronics and Applications*, 12(2) (2022), 34, DOI: https://doi.org/10.3390/jlpea12020034.

- 5. Gangineni, Manaswini, et al.; ±0.3 V Bulk-Driven Fully Differential Buffer with High Figures of Merit, *Journal of Low Power Electronics and Applications*, 12(3) (2022), 35 DOI: https://doi.org/10.3390/jlpea12030035.

- Mei, Shangming, et al; The Class D Audio Power Amplifier: A Review, *Electronics*, 11(19) (2022), 3244. DOI: https://doi.org/10.3390/electronics11193244

- Ketata, Ilef, et al.; Design and Implementation of Low Noise Amplifier Operating at 868 MHz for Duty Cycled Wake-Up Receiver Front-End, *Electronics*, 11(19) (2022), 3235. DOI: https://doi.org/10.3390/electronics11193235

- 8. Della Sala, Riccardo, Francesco Centurelli, Giuseppe Scotti, Pasquale Tommasino, and Alessandro Trifiletti; A Differential-to-Single-Ended

Converter Based on Enhanced Body-Driven Current Mirrors Targeting Ultra-Low-Voltage OTAs, *Electronics*, 11(23) (2022), 3838. DOI: https://doi.org/10.3390/electronics11233838

- Nandakishor Yadav, Youngbae Kim, Mahmoud Alashi and Kyuwon Ken Choi; Design of a voltage to time converter with high conversion gain for reliable and secure autonomous vehicles, *Electronics*, 9(3) (2020), 384. DOI: https://doi.org/10.3390/electronics9030384

- Aueamnuay, Chaiyanut, Ajmal Vadakkan Kayyil, Narayana Bhagirath Thota, Praveen Kumar Venkatachala and David J. Allstot; g m/I D-Based Frequency Compensation of CMOS Two-Stage Operational Amplifiers, *IEEE International Symposium on Circuits and Systems (ISCAS)*, (2020), 1-5. DOI: 10.1109/ISCAS45731.2020.9180575.

- Jianquan Hu and Kaixue Ma; Analysis and design of a broadband receiver front end for 0.1-to-40-GHz application, *IEEE Transactions on Circuits and Systems I: Regular Papers*, 68(6) (2021), 2393-2403. DOI: 10.1109/TCSI.2021.3064262.

- 12. SachchidaNand Shukla, Susmrita Srivastava; A New Circuit Model of Small-Signal Amplifier Using MOSFETs in Triple Darlington Topology, *International Journal of Modelling and Optimization*, 3(5) (2013), 394-398.

- R. Póvoa, N. Lourenço, R. Martins, A. Canelas, N. C. G. Horta and J. Goes; Single-Stage Amplifier Biased by Voltage Combiners with Gain and Energy-Efficiency Enhancement, *IEEE Transactions on Circuits and Systems II: Express Briefs*, 65(3) (2018), 266-270, DOI: 10.1109/TCSII.2017.2686586.

- 14. Ashraf Mohamed Ali Hassen; A Novel Circuit Model of Small-Signal Amplifier using MOSFETs and BJT in Quadruple Darlington Configuration, *International Journal of Computer Application*, 81(10), (2013), 26-30, DOI: 10.5120/14049-2214.

- 15. Syed Shamroz Arshad, SachchidaNand Shukla, Aditya Kumar Sharma, Geetika Srivastava; Darlington pair based Small-Signal amplifier under triple transistor topology, *Journal of International Academy of Physical Sciences*, 26(4), (2022), 427-442.

- 16. SachchidaNand Shukla, Syed Shamroz Arshad, Pratima Soni, Geetika Srivastava; Small Signal Amplifier with P-Type Sziklai Pair, *Journal of International Academy of Physical Sciences*, 24(3), (2020), 333–346.

- 17. SachchidaNand Shukla, Syed Shamroz Arshad, Pratima Soni, Geetika Srivastava, Ashish Dixit, Anil Kumar; Small-Signal Sziklai pair based Tuned Amplifiers with low power high gain, *Journal of International Academy of Physical Sciences*, 26(3), (2022), 281–361.

- 18. SachchidaNand Shukla, Syed Shamroz Arshad, Geetika Srivastava; NPN Sziklai pair small signal amplifier for high gain low noise submicron voltage

recorder, *International Journal of Power Electronics and Drive System*, 13(1) (2022), 11-22, DOI: 10.11591/ijpeds.v13.i1.pp11-22

19. SachchidaNand Shukla, Geetika Srivastava, Syed Shamroz Arshad; Study of Low-Noise Wide-Band Tuned Sziklai pair small-signal amplifier, *Research Trends and Challenges*, 1, (2021), 1-16, DOI: 10.9734/bpi/rtcps/v1/4064F.